Das sind so Sachen, die bringen mich ins Schleudern. Warum doppelt invertiert? Da kann mans doch gleich bleiben lassen?...

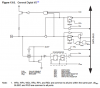

also ich interpretiere die kleinen Kreise an den Leitungen so. Der FET sperrt vielleicht nur bei 'nem high am Gate/Basis? Ist aber eigentlich nicht wichtig, entscheidend ist, daß das Und-Gatter festlegt, wann der Widerstand zum Pullup werden soll.

Warum muß hier PORTxn auf 1 sein? Der Port ist ja dann auf Input (DDRxn=0). Wodurch wird PORTxn gesetzt? Oder muß man das als rohes PINxn sehen?

reingefallen... PORTxn ist das n-te Bit des Registers PORTx. PORTx ist das Port Latch Register von Portx, und nicht zu verwechseln mit dem Data Direction Register von Portx (DDRx), klar. PORTx ist nicht (!) gleich Portx.

Wo hat denn dieses Gatter seine Ein- und wo seine Ausgänge? Und was macht es denn eigentlich?

Eingang ist der Ausgang des PORTxn D-Q-Latches.

Ausgang liegt auf dem Prozessorbeinchen. Es ist ein Treiber, der die Information des PORTxn in einen Pegel am Beinchen umsetzt. Achtung, der Ausgang des DDxn D-Q-Latches bedient den enable-Pin des Gatters.

Da ist noch so ein Teil, dessen Funktion mir nicht klar ist. Es sitzt links unten und sieht aus, wie zwei ineinander geschobene Dreiecke mit vier Anschlüssen.

Ist mir auch nicht ganz klar - deswegen bin ich auf Sleep auch nicht weiter eingegangen.

Das heißt, die Aussage "The Port Input Pins I/O location is read only, ..." ist nicht ganz richtig? Werden nur die , die eine 1 enthalten, oder alle? In der Documentation heißt es: "However, writing a logic one to a bit in the PINx Register, will result in a toggle in the corresponding bit in the Data Register."

Hast Die Antwort doch selbst druntergeschrieben...

Das PIN-Register ist read-only. Wenn Du versuchst, in eines der Bits eine eins zu schreiben (kopieren) (mit OUT, SBI, ST), wird diese nicht ins PIN-Register geschrieben (weils ja readonly ist), SONDERN stattdessen das korrespondierende Bit im ... genau genommen im entsprechenden PORT-Register muß da stehen ... getoggelt.

Ok, ich habe in den Schaltplänen von dino gesehen, daß PB7/8 mit XTAL1/2 verbunden ist. Was ich beim besten Willen nicht finden kann, ist die Beschaltung von PORTE/AUX.

PORTE/AUX ist "J704" in Sheet7 auf Seite 5 der pdf.

Und Du meinst sicher PB6/7

Was meinst Du mit "für etwas anderes"? PORTB6/7? Dann widerspricht das aber "When the XTAL1 jumper is not mounted, an external clock source or crystal can be connected to the PORTE header."

Der OSCSEL-Jumper verbindet entweder einen Oscillator, der mit einem Quarz festgelegt wird, oder einen softwaregenerierten Takt mit seinem Pin2. Dieser Pin kann über den XTAL1-Jumper mit dem XTAL1-Netz (also auch mit PB6 beim grünen Sockel) verbunden werden. Dann läßt sich der Prozessor mit einer externen Clock betakten (eben Software oder Hardware). Wenn der aber mit Seiner internen Clock läuft, und Du die Beinchen für irgendwas anderes (Taster, Leds, Whatever) benutzen willst, sind die ja im STK500 über den Sockel->XTAL1-Netz (inklusive PORTE-Header)->XTAL1-Jumper->OSCSEL-Jumper mit der Hardware/Software-Clock des STK500 verbunden, welche dann also ihren Takt an die LEDs/Taster/Whatever überträgt, klar?

Hängen denn die Zugriffsmöglichkeiten auf PORTB6/7 nicht auch davon ab, ob der Controller mit eigenem internen Takt arbeitet oder nicht. In ersterem Fall ist XTAL1 frei, im zweiten Fall nicht. Wenn man also einen externen Quarz anschließt sollte ein Zugriff auf PORTB6/7 ja nicht mehr möglich sein.

Achtung, Du wirfst den Controller und das STK durcheinander:

mit den Fusebiteinstellungen legst (hierbei) Du im Controller fest, ob PB6 und/oder PB7 normale I/O-Pins sein sollen, oder als Takteingang dienen sollen. Das hat aber keinen Einfluß auf die Verdrahtung des STK.

Da ist einmal die Variante, daß der Controller NICHT im STK500 steckt und mit einem Quarz beschaltet ist.

Dann gibt es die Variante im STK500 mit interner Versorgung (Quarzsockel oder MasterControler).

Und schließlich die Variante mit externem Takt im STK500 über PORTE.

Ich kann nicht überschauen, was das alles für die beiden hoherwertigen PORTB Pins bedeutet.

Nochmal, der Controller kann

-mittels internem RC-Oscillator betaktet werden, dann sind PB6 und PB7 freie I/Os

-mit unterschiedlichen Resonatoren/Quarzen Betaktet werden, dann werden die beiden Beinchen auf die Taktogik umgeschaltete (siehe oben "alternate functions")

-mit einer externen Clock (Quarzoszillator etc) betaktet werden, dafür wird nur PB6 verbraucht, PB7 bleibt I/O

Wie der Controller also mit den Impulsen an den Beinchen umgeht, hängt (in erster Linie) von den Fuses, und danach ggf vom Programm ab. Welche Signale/Impulse das STK auf die Beinchen legt, hängt von den Jumpern und der entsprechenden Einstellung um AVRStudio ab (Was der MasterController ausgeben soll, kann man da festlegen).

Bei mir ist der XTAL1 Jumper gesetzt und OSCSEL rechts (also auf 1,2). Demnach also eine Versorgung vom MasterControler. Die Fuses sitzen auf internem Takt, mit Vorteiler, so daß sich die Jumperpositionen nicht auswirken, oder?

Nein, Dein Controller läuft so mit dem internen Oscillator, der Takt, den der MasterC generiert wird über die beiden Jumper und den PORTE-Header an PB6 weitergeleitet. Wenn Du PB6 als Eingang verwendest, bekommst Du da das entsprechende Signal/die entsprechende Frequenz. Wie das/die zu interpretieren ist, ist Sache Deines Programmes - es hat nichts mehr mit der Taktlogik des Controllers zu tun. Wenn das aber ein Ausgang ist, könnte sogar ein Kurzschluß vorliegen - keine Ahnung, wie das abgesichert ist (wenn die Clock zB grad hi ist, und Du das Prozessorbeinchen auf Gnd schaltest)