Hallo Danke für den Tipp,

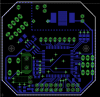

die Leiterbahn ist 0.6mm breit, sorry.

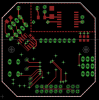

Die Pin-Belegung sollte stimmen, was ich nachträglich gemacht habe, ich habe die nicht benutzen Pins auf Masse gelegt.

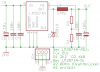

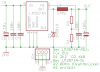

wie sollte deiner Meinung nach die Aufteilung der Kondensatoren aussehen,

ich habe im Internet verschiedenste Möglichkeiten gefunden.

z.B.:

Beste Grüße

die Leiterbahn ist 0.6mm breit, sorry.

Die Pin-Belegung sollte stimmen, was ich nachträglich gemacht habe, ich habe die nicht benutzen Pins auf Masse gelegt.

* No internal connection, but should be soldered to PC board for best heat transfer.

wie sollte deiner Meinung nach die Aufteilung der Kondensatoren aussehen,

ich habe im Internet verschiedenste Möglichkeiten gefunden.

z.B.:

Beste Grüße