Bascom BASCOM ; Erste Schritte zum Ausprobieren

- Ersteller Cassio

- Erstellt am

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Ja klar, dass du dabei nur im Streß stehst.

Du meinst bestimmt 3000MB. Aber macht nichts. Ich wollte nur wissen, weil das LCD I2C beim Arduino (hat ja einen Bootloader) funktioniert, dass es an meinem Programmer liegen kann. Dieser eventuell keinen I2C-Daten transportiert. Nur so ein Gedanke. Mit den Anweisungen von @Cassio I2C : LCD ( auch Arduino ) mit PCF8574 OHNE LIB betreiben funktioniert es auch nicht.

Hallo Heini-14

Ich kenne kein BASCOM, kann Dir also da nicht helfen, ich bin mir aber sicher, dass Deine Probleme nichts mit dem Programmer zu tun haben.

Der Programmer überträgt nur das Programm, dem ist es egal, was im Programm steht, solange es ein File ist, das im übertragbaren Format vorliegt und auf die Zielhardware geladen werden kann - will heißen, der "sieht" ja gar nicht, dass im Programm I2C-Daten vorhanden sind.

Wg I2C - da wurde ja schon in einem Beitrag auf die Adresse verwiesen - haste das mal kontrolliert? Die Adresse im Arduino ist vielleicht eine andere????

Hast Du Dich überhaupt schon mit I2C beschäftigt oder nur Files aus dem Internet gezogen? Kennst Du den Aufbau, Ablauf der Kommunikation, Adressierung des/der Teilnehmer etc? Ohne Wissen diesbezüglich wird es schwer, I2C zu verstehen.

Es wäre vielleicht sinnvoller und zielführender, wenn Du das Dir bislang erarbeitete Wissen vertiefst, bevor Du was komplett Neues beginnst (z.B. Ampel für Fußgänger UND Autofahrer, Ampel für Kreuzung, Anzeige Wartezeit, wenn Fussgänger die Ampel betätigt, Steuerung der Ampel über USART, Zeitvorgaben für die Ampelsteuerung per USART ändern usw).

Nur Wissen, das "sitzt", ist brauchbares Wissen.

Es bringt auch nicht viel, wenn man irgendwelche Codeschnipsel aus dem Internet zieht, ohne die Funktionen zu verstehen.

Um's mal mit der Schule zu vergleichen - Kinder lernen erst mal das "kleine Einmaleins", bevor sie mit Multiplikation etc beginnen.

Nichts für ungut - und lass Dich durch Rückschläge nicht entmutigen - nur durch (selbstgemachte) Fehler lernen wir

mfg

Hero_123

Ich kenne kein BASCOM, kann Dir also da nicht helfen, ich bin mir aber sicher, dass Deine Probleme nichts mit dem Programmer zu tun haben.

Der Programmer überträgt nur das Programm, dem ist es egal, was im Programm steht, solange es ein File ist, das im übertragbaren Format vorliegt und auf die Zielhardware geladen werden kann - will heißen, der "sieht" ja gar nicht, dass im Programm I2C-Daten vorhanden sind.

Wg I2C - da wurde ja schon in einem Beitrag auf die Adresse verwiesen - haste das mal kontrolliert? Die Adresse im Arduino ist vielleicht eine andere????

Hast Du Dich überhaupt schon mit I2C beschäftigt oder nur Files aus dem Internet gezogen? Kennst Du den Aufbau, Ablauf der Kommunikation, Adressierung des/der Teilnehmer etc? Ohne Wissen diesbezüglich wird es schwer, I2C zu verstehen.

Es wäre vielleicht sinnvoller und zielführender, wenn Du das Dir bislang erarbeitete Wissen vertiefst, bevor Du was komplett Neues beginnst (z.B. Ampel für Fußgänger UND Autofahrer, Ampel für Kreuzung, Anzeige Wartezeit, wenn Fussgänger die Ampel betätigt, Steuerung der Ampel über USART, Zeitvorgaben für die Ampelsteuerung per USART ändern usw).

Nur Wissen, das "sitzt", ist brauchbares Wissen.

Es bringt auch nicht viel, wenn man irgendwelche Codeschnipsel aus dem Internet zieht, ohne die Funktionen zu verstehen.

Um's mal mit der Schule zu vergleichen - Kinder lernen erst mal das "kleine Einmaleins", bevor sie mit Multiplikation etc beginnen.

Nichts für ungut - und lass Dich durch Rückschläge nicht entmutigen - nur durch (selbstgemachte) Fehler lernen wir

mfg

Hero_123

Zuletzt bearbeitet:

I2C habe ich mich schon befasst, aber nicht mit dem Wissen, dass notwendig ist. Wie ich oben schon erwähnte, habe ich auch die Themen mit I2C, auch von Cassio durchgenommen. Das Thema Adressen wäre hier eventuell die Lösung. Doch davon verstehe ich nichts.

Hallo Heini-14

Es gibt über I2C und die Adressen (READ - WRITE) sehr viel im Internet, und Wissenslücken kannst Du damit auch zu füllen versuchen. Da musst Du aber auch selbst tätig werden.

Es ist doch nicht zielführend, wenn Du von jemand eine mehr oder weniger fertige Lösung bekommst/übernimmst, sie aber nicht verstehst bzw das damit vermittelte Wissen nicht anwendest / anwenden kannst.

Nichts für ungut

mfg

Hero_123

Nachtrag: anbei ein paar links:

rn-wissen.de

rn-wissen.de

rn-wissen.de

rn-wissen.de

github.com

github.com

www.technoblogy.com

www.technoblogy.com

I2C habe ich mich schon befasst, aber nicht mit dem Wissen, dass notwendig ist. Wie ich oben schon erwähnte, habe ich auch die Themen mit I2C, auch von Cassio durchgenommen. Das Thema Adressen wäre hier eventuell die Lösung. Doch davon verstehe ich nichts.

Es gibt über I2C und die Adressen (READ - WRITE) sehr viel im Internet, und Wissenslücken kannst Du damit auch zu füllen versuchen. Da musst Du aber auch selbst tätig werden.

Es ist doch nicht zielführend, wenn Du von jemand eine mehr oder weniger fertige Lösung bekommst/übernimmst, sie aber nicht verstehst bzw das damit vermittelte Wissen nicht anwendest / anwenden kannst.

Nichts für ungut

mfg

Hero_123

Nachtrag: anbei ein paar links:

TWI – RN-Wissen.de

I2C – RN-Wissen.de

ArduinoCore-avr/libraries/Wire/src/utility at master · arduino/ArduinoCore-avr

The Official Arduino AVR core. Contribute to arduino/ArduinoCore-avr development by creating an account on GitHub.

Technoblogy - Making Your Own I2C Peripherals

Anhänge

Zuletzt bearbeitet:

TommyB

Team Bitschubse

Und ich lag im Krankenhaus...

Und ich hatte schon einiges versucht hier zu vermitteln, auch das mit den Adressen.

Und: 300MB sind keine Seltenheit. Ich selbst hab nur 1GB mobil.

Und ich hatte schon einiges versucht hier zu vermitteln, auch das mit den Adressen.

Und: 300MB sind keine Seltenheit. Ich selbst hab nur 1GB mobil.

Ich hoffe es ist nichts ernstes. Auf jeden Fall wünsche ich Dir eine Gute Besserung.

Ich habe immer noch Probleme mit meinem Arm, den ich kurz vor dem Urlaub verletzt habe. Letztendlich wird er heute operiert (nur Schleimbeutel entfernen).

Ich habe immer noch Probleme mit meinem Arm, den ich kurz vor dem Urlaub verletzt habe. Letztendlich wird er heute operiert (nur Schleimbeutel entfernen).

Hallo Heini,

es gibt bei einer Schnittstelle/Bus/Interface/... immer mehrere Dinge die man beachten muß und die man im Kopf und bei der Fehlersuche trennen sollte.

- Das elektronische der Schnittstelle (Anzahl Leitungen, Pegel/Spannungen, Welcher Pegel steht für 1 und welcher für 0, OpenCollector oder Tristate oder Gegentakt)

- die zeitliche Abfolge der Signale/Pegel/Bits (Start der Übertragung, Ende der Übertragung, Bestätigungen, Adressen, Daten, Abfolge der Bits - kleinstes oder größtes zuerst, ...)

- das logische Protokoll (wie wird schreiben/lesen durchgeführt - elektrisch mit einer Leitung oder mit einem Bit, wie werden Adressen aufgebaut, wie werden die Daten übertragen, ...)

I2C:

Das ist ein Bussystem mit 2 signalführenden Leitungen SCL Serial Clock + SDA Serial Data (TWI = Two Wire Interface) UND natürlich GND. Die Bausteine sind mit OpenCollector-Anschlüssen an das Bussystem gekoppelt. Damit man also nicht nur GND hat wenn die Ausgänge durchschalten benötigt man bei BEIDEN Leitungen an EINER Stelle am Bus JEWEILS einen PullUp-Widerstand. Ich nehme 4,7kOhm. Manche nehmen 10kOhm. Sollte für einen kurzen Bus beides funktionieren. Der RASPI kann nur 3,3V bei I2C vertragen. Der Atmel normalerweise 5V (kommt IMMER auf die Betriebsspannung ALLER Busteilnehmer an). Wenn man Teilnehmer mit verschiedenen Versorgungsspannungen verwenden möchte, dann benötigt man eine Pegelanpassung zwischen den 3,3V- und den 5V Busteilnehmern und für beide Zweige jeweils PullUps.

GND-Pegel heißt das Bit ist auf 0, positiver Pegel über die PullUps bedeutet eine 1. Die beiden Leitungen vom Bus sind im Ruhezustand beide auf High (3,3V oder 5V). Um die Start- oder Stop-Bedingung am Bus anzuzeigen, wird vom Master eine normalerweise nicht genehmigte Signalabfolge der beiden Leitungen verwendet. Im Normalfall, darf sich der Pegel der Datenleitung nicht ändern, wenn die Taktleitung auf High liegt. Die Startbedingung wird vom Busmaster erzeugt, wenn er die Datenleitung nach GND/Low zieht, wenn die Taktleitung noch auf High liegt. Die Stopbedingung erzeugt der Master, wenn er bei High auf der Taktleitung die Datenleitung wieder auf High wechseln läßt. Den Takt erzeugt im Normalfall der Busmaster.

Die Adressen und Daten sind alle 8Bit (also 1 Byte). Die Adressen sind dabei aber ein wenig speziell ...

Das unterste Bit (Bit0) der Adresse ist für die Meldung ob der Master vom Busteilnehmer lesen oder schreiben möchte. Die Bits 1-7 sind die eigentliche Adresse.

Beispiel ... PCF8574 - 8Bit paralleles Busregister/Portbaustein

Grundadresse hex 20 (für die oberen 7 Bits! also 7 bis 1) wenn A2, A1 und A0 am IC auf GND liegen (die beeinflussen die unten 3 Bits der Adresse!)

010 0000 = hex 20 (durchzählen! es sind 7 Bit!)

Das unterste Bit0 wird für Read/Write verwendet. Also Read = 1 und Write = 0. Das ergibt dann mit der 7Bit Adresse folgende 8Bit-Adressen ...

010 0000 0 = hex 40 für Write - Die 8Bit-Schreibadresse des Bausteins

010 0000 1 = hex 41 für Read - Die 8Bit-Leseadresse des Bausteins

Um die Verwirrung für den Benutzer komplett zu machen, geben manche Hersteller im Datenblatt als Adresse die obersten 7 Bits (Bit7-1) an und manche Hersteller die vollständigen 8Bit Schreib- und Leseadressen.

Die Adresse ist also folgendermaßen beim PCF8574 aufgebaut ...

0 - 1 - 0 - 0 - A2 - A1 - A0 - R/W

Die 7Bit Grundadresse (Bit 7-1) kann sich also zwischen hex 20 (A2-0 auf GND) und hex 27 (A2-0 auf +5V) bewegen. Damit kann man also 7 dieser ICs am Bus betreiben, da die Adressen nicht doppelt verwendet werden dürfen. Sieh dir mal das Datenblatt an ...

https://www.mikrocontroller.net/part/PCF8574 ... Seite 12 + 13

Das sollte für das erste Verständnis hoffentlich reichen.

Gruß

Dino

Das Thema Adressen wäre hier eventuell die Lösung. Doch davon verstehe ich nichts.

es gibt bei einer Schnittstelle/Bus/Interface/... immer mehrere Dinge die man beachten muß und die man im Kopf und bei der Fehlersuche trennen sollte.

- Das elektronische der Schnittstelle (Anzahl Leitungen, Pegel/Spannungen, Welcher Pegel steht für 1 und welcher für 0, OpenCollector oder Tristate oder Gegentakt)

- die zeitliche Abfolge der Signale/Pegel/Bits (Start der Übertragung, Ende der Übertragung, Bestätigungen, Adressen, Daten, Abfolge der Bits - kleinstes oder größtes zuerst, ...)

- das logische Protokoll (wie wird schreiben/lesen durchgeführt - elektrisch mit einer Leitung oder mit einem Bit, wie werden Adressen aufgebaut, wie werden die Daten übertragen, ...)

I2C:

Das ist ein Bussystem mit 2 signalführenden Leitungen SCL Serial Clock + SDA Serial Data (TWI = Two Wire Interface) UND natürlich GND. Die Bausteine sind mit OpenCollector-Anschlüssen an das Bussystem gekoppelt. Damit man also nicht nur GND hat wenn die Ausgänge durchschalten benötigt man bei BEIDEN Leitungen an EINER Stelle am Bus JEWEILS einen PullUp-Widerstand. Ich nehme 4,7kOhm. Manche nehmen 10kOhm. Sollte für einen kurzen Bus beides funktionieren. Der RASPI kann nur 3,3V bei I2C vertragen. Der Atmel normalerweise 5V (kommt IMMER auf die Betriebsspannung ALLER Busteilnehmer an). Wenn man Teilnehmer mit verschiedenen Versorgungsspannungen verwenden möchte, dann benötigt man eine Pegelanpassung zwischen den 3,3V- und den 5V Busteilnehmern und für beide Zweige jeweils PullUps.

GND-Pegel heißt das Bit ist auf 0, positiver Pegel über die PullUps bedeutet eine 1. Die beiden Leitungen vom Bus sind im Ruhezustand beide auf High (3,3V oder 5V). Um die Start- oder Stop-Bedingung am Bus anzuzeigen, wird vom Master eine normalerweise nicht genehmigte Signalabfolge der beiden Leitungen verwendet. Im Normalfall, darf sich der Pegel der Datenleitung nicht ändern, wenn die Taktleitung auf High liegt. Die Startbedingung wird vom Busmaster erzeugt, wenn er die Datenleitung nach GND/Low zieht, wenn die Taktleitung noch auf High liegt. Die Stopbedingung erzeugt der Master, wenn er bei High auf der Taktleitung die Datenleitung wieder auf High wechseln läßt. Den Takt erzeugt im Normalfall der Busmaster.

Die Adressen und Daten sind alle 8Bit (also 1 Byte). Die Adressen sind dabei aber ein wenig speziell ...

Das unterste Bit (Bit0) der Adresse ist für die Meldung ob der Master vom Busteilnehmer lesen oder schreiben möchte. Die Bits 1-7 sind die eigentliche Adresse.

Beispiel ... PCF8574 - 8Bit paralleles Busregister/Portbaustein

Grundadresse hex 20 (für die oberen 7 Bits! also 7 bis 1) wenn A2, A1 und A0 am IC auf GND liegen (die beeinflussen die unten 3 Bits der Adresse!)

010 0000 = hex 20 (durchzählen! es sind 7 Bit!)

Das unterste Bit0 wird für Read/Write verwendet. Also Read = 1 und Write = 0. Das ergibt dann mit der 7Bit Adresse folgende 8Bit-Adressen ...

010 0000 0 = hex 40 für Write - Die 8Bit-Schreibadresse des Bausteins

010 0000 1 = hex 41 für Read - Die 8Bit-Leseadresse des Bausteins

Um die Verwirrung für den Benutzer komplett zu machen, geben manche Hersteller im Datenblatt als Adresse die obersten 7 Bits (Bit7-1) an und manche Hersteller die vollständigen 8Bit Schreib- und Leseadressen.

Die Adresse ist also folgendermaßen beim PCF8574 aufgebaut ...

0 - 1 - 0 - 0 - A2 - A1 - A0 - R/W

Die 7Bit Grundadresse (Bit 7-1) kann sich also zwischen hex 20 (A2-0 auf GND) und hex 27 (A2-0 auf +5V) bewegen. Damit kann man also 7 dieser ICs am Bus betreiben, da die Adressen nicht doppelt verwendet werden dürfen. Sieh dir mal das Datenblatt an ...

https://www.mikrocontroller.net/part/PCF8574 ... Seite 12 + 13

Das sollte für das erste Verständnis hoffentlich reichen.

Gruß

Dino

Zuletzt bearbeitet:

Wenn ich das mit dieser Adresse richtig verstanden habe, müsste die in Zeile 8 richtig sein. Tut es aber nicht. Also liegt der Fehler nicht nur ander Adresse.0 - 1 - 0 - 0 - A2 - A1 - A0 - R/W

CodeBox BascomAVR

$regfile = "m8def.dat" 'ATMega8 $crystal = 8000000 '8 MHz $lib "YwRobot_Lcd_i2c.lib" 'YwRobot Treiber für LCD $hwstack = 64 $swstack = 10 $framesize = 40 '******************* Deklarationen ************************ Const Pcf8574_lcd = &H40 'Adresse des I2C-LCDs A0 - A2 =0 Dim Lcd_backlight As Byte '1 = an; 0 = aus. Wird erst durch einen LCD-Befehl umgesetzt! '****************** Initialisierung *********************** Config Scl = Portc.5 'Konfigurieren von I2C Config Sda = Portc.4 Config Lcd = 16 * 2 'nicht unbedingt nötig Config I2cdelay = 1 Waitms 300 'warte bis LCD-Initialisiert ist! '******************** Hauptprogramm *********************** Cls Lcd "Hallo BASCOM LK" Wait 1 Lcd_backlight = 0 Locate 2 , 1 Lcd "Thanks for help" Wait 2 Lcd_backlight = 1 Locate 1 , 1 'Damit Backlight-Zustand an LCD übermittelt wird Do nop Loop End

In Beitrag #749 schrieb ich schon, daß der PCF8574 nur 100 kHz kann und nicht 1 MHz, wie mit der obigen Zeile eingestellt wird.Config I2cdelay = 1

@Hero_123 hat mal gesagt,

Die wäre, wo kommt die 32 bei der Berechnung des Overflow, Systemtakt / 16Bit * Prescaler, her?

Prescaler 1, 8, 64, 256, 1024.

Ich habe diese aus einer PDF-Datei Was ist ein Timer?, Allgemeine Funktionsweise, Prescaler usw.

Also werde ich erst einmal Fragen zum bisher gelernten stellen.Analogie zum Kind - wenn es gerade das Laufen lernt, ist ein 100m Lauf .... utopisch - und das gilt HIER genauso

Die wäre, wo kommt die 32 bei der Berechnung des Overflow, Systemtakt / 16Bit * Prescaler, her?

Prescaler 1, 8, 64, 256, 1024.

Ich habe diese aus einer PDF-Datei Was ist ein Timer?, Allgemeine Funktionsweise, Prescaler usw.

TommyB

Team Bitschubse

Comic Sans...... Naja, egal.

Obacht! Nicht jeder Controller kann jeden Vorteiler!

Da musst du denn schon im Datenblatt nachschauen. Beispiel Mega8, Timer1:

Seite 99 (Register description / Clock source.

Andere können vielleicht /32, dafür aber nicht /1024, etc.

Dir stehen also nur clk/1 (=8MHz - gehe ich von aus), /8 (=1MHz), /64 (=125kHz), /256 (=31,25kHz) und /1024 (=7,8125kHz) zur Verfügung.

Rechnung ist simpel, CPU Frequenz / Vorteiler. Das wäre die Frequenz mit der der Timer getaktet wird.

Sagen wir du nutzt /8 bei 8MHz, also effektiv 1MHz für den Timer. Sprich der Wert erhöht sich 1 Million Mal pro Sekunde.

Sprich 1 (Sekunde) / 1.000.000 (Timer Frequenz in Hz) = 0,000001 Sekunden = 0,001mS = 1µS

Also verstreicht pro Tick 1µS.

Jetzt hast du im Timer entweder ein variables Limit (innerhalb der Grenzen) was du selber definieren kannst (CTC), oder spätestens halt das Hardware Limit (256 Ticks bei 8 Bit, 65536 bei 16 Bit).

Wenn selbst das dir noch zu schnell ist, niemand hindert dich daran per Software weiter zu teilen, um z.B. auf Minutenintervalle zu kommen. Du erinnerst dich an Tick_1s?

Eigentlich hatten wir alles schon mal, wo hängst du fest?

Aufgabe:

Gegeben: Mega8, 8MHz.

Frage: Was ist das langsamste Intervall was du (per Hardware) einstellen könntest? Angabe in Sekunden.

Obacht! Nicht jeder Controller kann jeden Vorteiler!

Da musst du denn schon im Datenblatt nachschauen. Beispiel Mega8, Timer1:

Seite 99 (Register description / Clock source.

Andere können vielleicht /32, dafür aber nicht /1024, etc.

Dir stehen also nur clk/1 (=8MHz - gehe ich von aus), /8 (=1MHz), /64 (=125kHz), /256 (=31,25kHz) und /1024 (=7,8125kHz) zur Verfügung.

Rechnung ist simpel, CPU Frequenz / Vorteiler. Das wäre die Frequenz mit der der Timer getaktet wird.

Sagen wir du nutzt /8 bei 8MHz, also effektiv 1MHz für den Timer. Sprich der Wert erhöht sich 1 Million Mal pro Sekunde.

Sprich 1 (Sekunde) / 1.000.000 (Timer Frequenz in Hz) = 0,000001 Sekunden = 0,001mS = 1µS

Also verstreicht pro Tick 1µS.

Jetzt hast du im Timer entweder ein variables Limit (innerhalb der Grenzen) was du selber definieren kannst (CTC), oder spätestens halt das Hardware Limit (256 Ticks bei 8 Bit, 65536 bei 16 Bit).

Wenn selbst das dir noch zu schnell ist, niemand hindert dich daran per Software weiter zu teilen, um z.B. auf Minutenintervalle zu kommen. Du erinnerst dich an Tick_1s?

Eigentlich hatten wir alles schon mal, wo hängst du fest?

Aufgabe:

Gegeben: Mega8, 8MHz.

Frage: Was ist das langsamste Intervall was du (per Hardware) einstellen könntest? Angabe in Sekunden.

TommyB

Team Bitschubse

Du setzt doch den Prescaler in Bascom über den Config Befehl. Warum willst du jetzt direkt an den Registern rum fummeln?

Config Timer0 = Timer , Prescale = 64

!

Config Timer0 = Timer , Prescale = 64

!

Ich habe die Aufgabe ganz übersehen.

Na ja, ich will lernen, die Register zu verstehen. Wusste doch nicht, dass das (1<<WGM01) Prescaler=64 bedeutet.Warum willst du jetzt direkt an den Registern rum fummeln?

TommyB

Team Bitschubse

Tut es auch nicht.*

WGM01 ist eins von den 8 Bits die die Taktquelle des Timers steuern.

Welches Bit was bedeutet muss man dann im Datenblatt nachschlagen, da das je nach Chip unterschiedlich sein kann. Daher nein, bedeutet es nicht. Aber das Bit ansich ist schon die richtige Richtung (WGMxy = Waveform Generation Mode - Timer x - Bit y). Siehe den letzten Auszug aus dem Datenblatt. Es kann auch sein dass /64 gar nicht existiert, oder dafür WGM10 statt WGM11 gesetzt werden muss.

Man gewöhnt sich recht schnell an die Abkürzungen. Aber wozu, wenn dir Bascom eh (fast) alles abnimmt?

Ja, ne, ich meine was wäre die maximale Zeitspanne die du erreichen könntest, nicht was du möchtest, sondern was Hardwaretechnisch maximal möglich ist.

Preload würde ich übrigens vermeiden wo es nur geht, lieber CTC - oder Normalbetrieb, falls du mit ggf. krummen Werten klar kommst, also das erreichst was du willst.

Warum Preload suboptimal ist klären wir dann später, falls du nicht von allein drauf kommst.

.

WGM01 ist eins von den 8 Bits die die Taktquelle des Timers steuern.

Welches Bit was bedeutet muss man dann im Datenblatt nachschlagen, da das je nach Chip unterschiedlich sein kann. Daher nein, bedeutet es nicht. Aber das Bit ansich ist schon die richtige Richtung (WGMxy = Waveform Generation Mode - Timer x - Bit y). Siehe den letzten Auszug aus dem Datenblatt. Es kann auch sein dass /64 gar nicht existiert, oder dafür WGM10 statt WGM11 gesetzt werden muss.

Man gewöhnt sich recht schnell an die Abkürzungen. Aber wozu, wenn dir Bascom eh (fast) alles abnimmt?

Ja, ne, ich meine was wäre die maximale Zeitspanne die du erreichen könntest, nicht was du möchtest, sondern was Hardwaretechnisch maximal möglich ist.

Preload würde ich übrigens vermeiden wo es nur geht, lieber CTC - oder Normalbetrieb, falls du mit ggf. krummen Werten klar kommst, also das erreichst was du willst.

Warum Preload suboptimal ist klären wir dann später, falls du nicht von allein drauf kommst.

.

Dazu wollt ich eigentlich fragen, was der Unterschied ist, den Sekundentakt wie in #109 und der mit Preloader, der allerdings ganz genau ist.Warum Preload suboptimal ist klären wir dann später, falls du nicht von allein drauf kommst.

Übrigens habe in #97 diese Erklärungen gehabt, mit dem ich überhaupt nichts anfangen konnte. Sieht jetzt schon etwas besser aus.

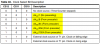

Es werden in folgenden drei Registern Bits gesetzt:

- DDRB: &B00000110

- TCCR1A: &B11110001

- TCCR1B: &B00000011

- B1 und B2 werden Ausgänge (11)

- Waveform Generation Mode für Timer 1 wird WGM=&B0001

- Compare Output Mode für beide Kanäle: COM1A[1..0]=&B11, COM1B[1..0]=&B11

- Clock Select CS=&B011, das entspricht Prescaler=64

Also bei Taktfrequenz 8Mhz und ohne Vorteiler, Timer1 komme ich auf 83,89ms. Aber warum diese Aufgabe.

Ich hänge nicht fest, ich habe das ganze noch nie richtig praktisch austesten können. Ich meine das so, was passiert, wenn ich dies und jenes im Code ändere. Was machen dann die LED's, oder der Piepser auf dem Steckbrett. Ich brauche halt immer praktische bzw. optische Vergleiche. Ich muss sehen, was die verschiedenen Anweisungen im Code anstellen.Eigentlich hatten wir alles schon mal, wo hängst du fest?