Hallo zusammen,

ich habe da ein Problem, wo ich nicht weiß, wie ich das lösen soll...

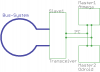

UseCase: Ein Bussystem mit mehreren Knoten, einer davon ist mein Modul. Das Modul ist ein Odroid-Board mit der Anbindung an dieses Bussystem. Der Transceiver spricht "nach Aussen" (also zum Host-Controller) I²C.

Das Problem: Das Bussystem setzt voraus, dass die Knoten, die sich auf dem Bus befinden, innerhalb einer gewissen Zeit nach dem Power-On oben und angemeldet sind... Der Busmaster hält die Knotenliste vor, deswegen ist die "nachträgliche" Anmeldung nicht drin. Hier ist es aber so, dass Odroid eine Weile zum Booten braucht... und somit diese Zeit verstreicht...

Meine Idee: Man nehme ein Atmega, Attiny, oder sonstwas und lasse den Transceiver von ihm hochfahren, das Anmelden erledigt und etc. Dann, wenn Odroid hochgefahren ist, übernimmt er die Steuerung vom Transceiver (Odroid meldet sich beim Atmega und sagt ihm, dass er ab jetzt off-line ist). Es wäre dann ein MultiMaster-System, bei dem nur ein Master aktiv ist...

Kann das funktionieren?

ich habe da ein Problem, wo ich nicht weiß, wie ich das lösen soll...

UseCase: Ein Bussystem mit mehreren Knoten, einer davon ist mein Modul. Das Modul ist ein Odroid-Board mit der Anbindung an dieses Bussystem. Der Transceiver spricht "nach Aussen" (also zum Host-Controller) I²C.

Das Problem: Das Bussystem setzt voraus, dass die Knoten, die sich auf dem Bus befinden, innerhalb einer gewissen Zeit nach dem Power-On oben und angemeldet sind... Der Busmaster hält die Knotenliste vor, deswegen ist die "nachträgliche" Anmeldung nicht drin. Hier ist es aber so, dass Odroid eine Weile zum Booten braucht... und somit diese Zeit verstreicht...

Meine Idee: Man nehme ein Atmega, Attiny, oder sonstwas und lasse den Transceiver von ihm hochfahren, das Anmelden erledigt und etc. Dann, wenn Odroid hochgefahren ist, übernimmt er die Steuerung vom Transceiver (Odroid meldet sich beim Atmega und sagt ihm, dass er ab jetzt off-line ist). Es wäre dann ein MultiMaster-System, bei dem nur ein Master aktiv ist...

Kann das funktionieren?